Appearance

第 6 章:示例项目

来源:

mystic_ug.pdf(W‑2024.09),Chapter 6 Mystic Examples。

官方随发行包提供一套 14 nm FinFET 示例,演示多阶段提取、批量脚本与 Sentaurus Visual 绘图。本章总结示例文件位置、运行前提,以及三阶段(低漏电 Id‑Vg、高漏电 Id‑Vg/Id‑Vd、C‑V)执行流程与产出。

6.1 示例位置与运行前提

- 路径:

$STROOT/tcad/$STRELEASE/manuals/tcad_spice/mystic_api/examples/。 - 环境检查:

- 确认 Mystic / PrimeSim HSPICE 已在

PATH且许可证可用:bashMystic --version primesim --version # 如需 SNPSLMD_LICENSE_FILE应指向可用许可证服务器。

- 确认 Mystic / PrimeSim HSPICE 已在

- 运行方式:示例通过命令行运行 Mystic,绘图使用 Sentaurus Visual (

svisual) 搭配提供的.tcl脚本。 - 文件夹结构(解压 14nmFinFET.zip 后):

models/:nmos.mod(BSIM-CMG 子电路,含默认参数)。strategies/:三阶段 Python 脚本(ld_extraction.py、hd_extraction.py、cv_extraction.py)及配套plot_*.tcl。targets/:I‑V、C‑V 目标数据。results/:输出目录(空,供写入拟合结果与模型卡)。

每阶段结束后会写一个新的模型卡,供下一阶段作为

--model输入,确保参数沿流程逐步收敛。

6.2 第一阶段:低漏电 Id‑Vg

- 目的:拟合低漏电偏置下的 Id‑Vg 曲线,为后续阶段提供初始模型。

- 命令:bash

Mystic strategies/ld_extraction.py --model=models/nmos.mod - 典型终端输出:

- 显示版本、加载的策略/模型/后端等信息。

Fitting Result Data中记录优化参数(如mosmod.PHIG、mosmod.CDSC)、迭代次数、fit error、收敛状态、耗时等。

- 结果:

- 拟合后的模型卡写入

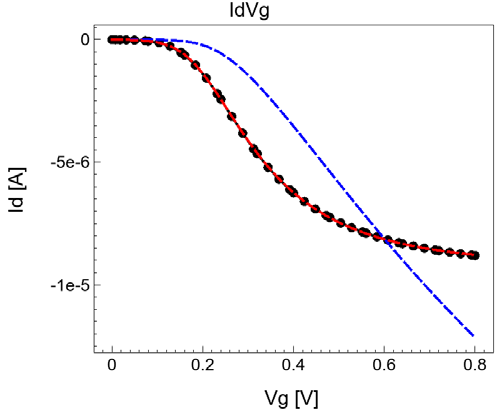

results/(例如nmos-ld.mod)。 - 使用 Sentaurus Visual 查看:

svisual strategies/plot_ld.tcl(图 50)。 - 该模型作为第二阶段输入。

- 拟合后的模型卡写入

6.3 第二阶段:高漏电 Id‑Vg / Id‑Vd

- 目的:在低漏电拟合基础上,同时校准高漏电 Id‑Vg 与多条 Id‑Vd 曲线。

- 命令:bash

Mystic strategies/hd_extraction.py --model=models/nmos-ld.mod - 特点:参数和目标更多,执行时间较长。策略完成后:

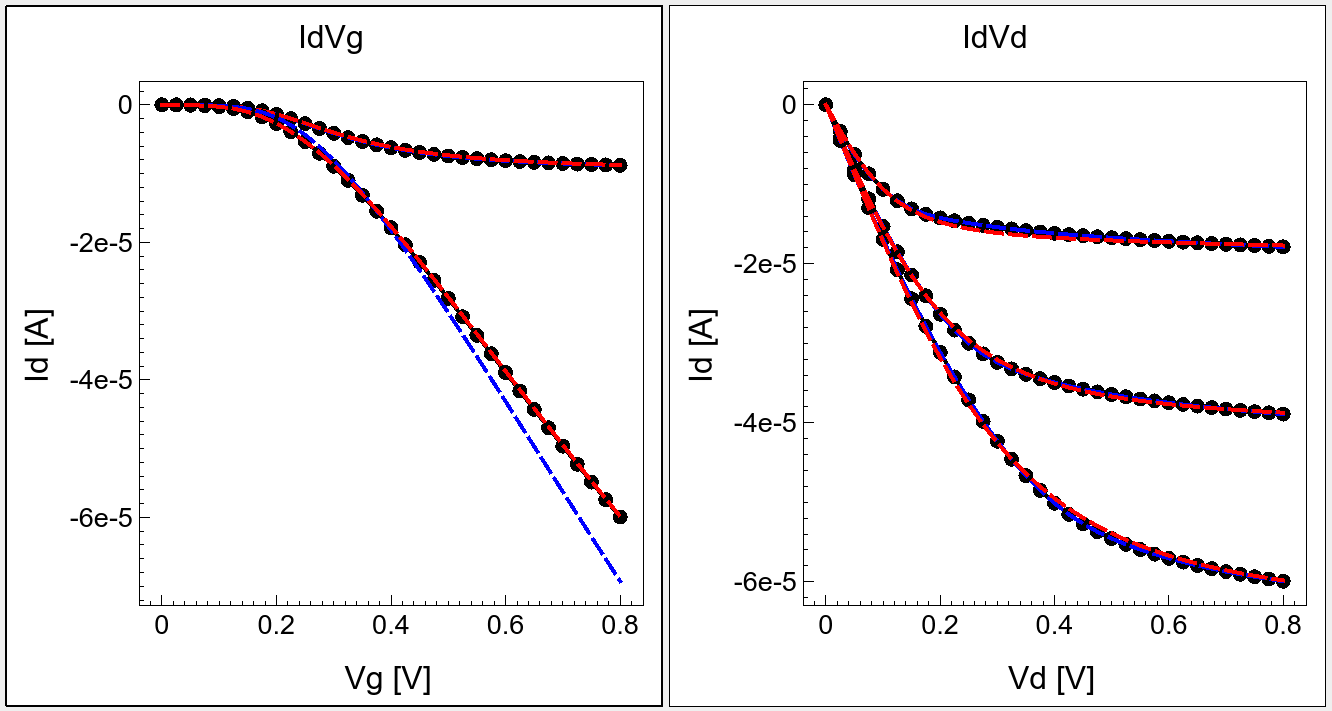

svisual strategies/plot_hd.tcl可同时显示高漏电 Id‑Vg 与 Id‑Vd(图 51),初始条件可观察低漏电阶段遗留的拟合质量。results/中生成新的模型卡(示例命名nmos-hd.mod),供 C‑V 阶段使用。

6.4 第三阶段:C‑V

- 目的:拟合门电容曲线,完善模型静电行为。

- 命令:bash

Mystic strategies/cv_extraction.py --model=models/nmos-hd.mod - 流程:结构与前两阶段类似,但目标为 C‑V。C‑V 数据格式 Mystic 已内建支持,无需特殊处理。

- 验证:

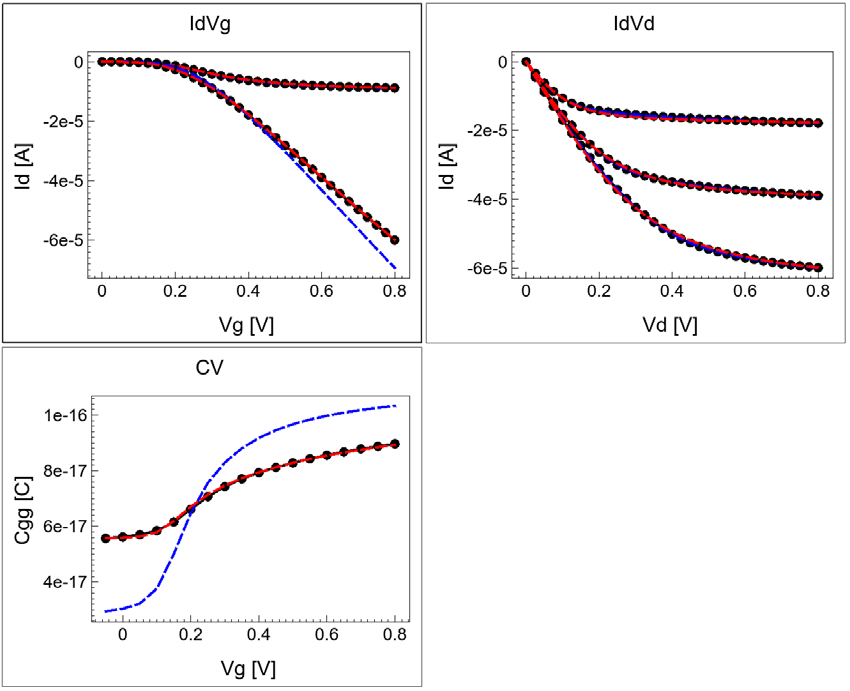

svisual strategies/plot_cv.tcl同时展示三类目标(低漏电、高漏电、C‑V,图 52)。- 最终模型写入

models/nmos-final.mod,可直接用于 PrimeSim HSPICE 仿真或后续流程。

除 14 nm FinFET 示例外,其它演示项目与脚本也包含在

examples/目录,可作为自定义流程的模板。